Artikel nieuwsbrief maart 2009 van de Benelux QRP club.

Nieuwe ontwikkelingen van Local oscillators.

Vorig jaar kwam ik in ELEKTUUR een bericht tegen over een programmeerbare klokoscillator de Si570 van silabs, toen al was ik gecharmeerd van de opzet.

Maar beperkte gegevens en onbekende verkrijgbaarheid, hebben dat idee in de ijskast geplaatst.

Vele zendamateurs, vooral in de VS en in Duitsland hebben zich nu op dit onderdeel gestort.

Het onderdeel is nu via de amateur verenigingen goed verkrijgbaar. (1)

Deze hybride module is niet voor ons gemaakt, maar als hoogwaardige klokgenerator in moderne apparatuur.(2)

Omdat er steeds meer ontwerpen met deze interessante module komen wil ik wat meer informatie geven over de technische achtergronden van het ding.

Deze kleine smd module herbergt een kompleet afstemsysteem dat via de I2C bus geprogrammeerd kan worden.

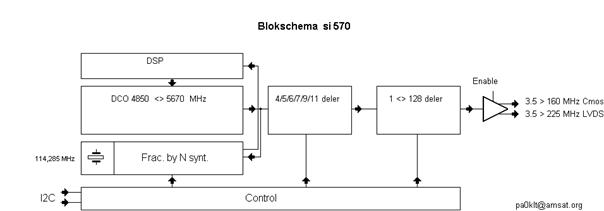

De interne klok van 114,285 MHz, die als referentie wordt gebruikt voor een PLL met een microgolf VCO van 4850 tot 5870 MHz en een programmeerbare deler die direct de 114,285 MHz als reverentie gebruikt.

Deze hoge vergelijkfrequentie, laat een grote PLL bandbreedte toe waardoor de VCO opgeschoond wordt door de kristal klok en mede daardoor een relatief lage faseruis produceert.

Omdat een stapgrote van 114,285 MHz natuurlijk veel te hoog is, wordt een fraction by N synthesizer toegepast. (3/4/5/6)

Wat is een fractional N divider:

Deze techniek werd in de tachtiger jaren al toegepast in digitale signaalgenerators die met stapjes van een hertz moesten kunnen worden ingesteld.

Ook de bekende 10/11 en 128/129 delers gebruiken deze techniek, waarin te tellen pulsen worden ingeslikt.

Als je over een lange periode en aantal keren het deeltal met een verhoogd, kan je oneindig kleine stappen maken.

Maar ja, elk voordeel heeft ook nadelen.

Bij deze methode ontstaan fase sprongen, die bij elke fractie van de deler anders zijn.

Deze fasesprongen zullen tot een instabiele PLL lijden.

Om dit op te lossen, moest er heel veel worden toegevoegd aan de deler.

Ik ben niet zo goed in wiskunde, maar in het kort komt het er op neer, dat er een aantal deeltallen worden toegevoegd, die over de gehele deelperiode als resultaat nul hebben.

De fasesprongen worden als ware gemaskeerd door de vele “dode” sprongen en het geheel wordt een ruis die als het aantal toevoegingen groot genoeg is, zo hoog in frequentie dat dit in de PLL wordt weggeregeld.

In 2003 heeft ur3iqo (7) dit systeem toegepast in een tranciver en daarmee een resultaat bereikt die vergelijkbaar was met de oudere generatie DDS IC’s en een PLL.

Hij gebruikte niet een grote hoeveelheid TTL schakelingen, maar een moderne CPLD (8) die hij geprogrammeerd heeft.

In de Si570 wordt deze techniek van schonen niet gebruikt, maar een door silicon labs ontwikkelde techniek met een DCO (digitally-controlled oscillator) en een moderne DSP, wordt jitter compensatie toegepast.

De PLL heeft een 10 bit deler voor de 114,285 MHz stappen waarvan alleen de deeltalen 42 t/m 51 worden gebruikt en een 28 bit deler voor de fractie het getal achter de komma.

De kleinste afstemstappen zijn dus 114,285 MHz / 2^28 = 0,426 Hz over het hele bereik en deze stappen worden nog verkleind door de HS maal de N deler.

De PLL geregelde VCO frequentie wordt namelijk nog gedeeld met de HS en de N deler naar bruikbare waarden.

De HS deler kan geprogrammeerd worden met de deeltallen 4,5,6,7,9 en 11

De N deler kan door 1,2,4,6,8 …… 128 delen dus alleen even deeltallen.

Met deze deeltallen kan altijd een combinatie gemaakt worden, die de VCO frequentie naar een geschikte uitgangsfrequentie deelt.

Voorbeeld:

Voor een frequentie 10 MHz en de 6 en 84 deler moet het VCO geprogrammeerd worden op 10 * 6 * 84 = 5040 MHz

De N deler moet dan geprogrammeerd worden met het getal 5040/114,285 = 44,10027563

Het schone VCO signaal (5040 MHz) wordt in dit voorbeeld nog eens door 504 (6*84) gedeeld wat het signaal nog verder verbeterd.

Het resultaat is een uitgangssignaal dat in kwaliteit gelijk is, als dat van een modern DDS IC zoals de AD9951 met een schoon 400 MHz kloksignaal dus zonder interne klokvermenigvuldiging.

Deze module wordt vooral ingezet als kristalvervanger voor elke willekeurige frequentie maar ook uitstekend bruikbaar voor SDR toepassingen waar de fijnafstemming softwarematig plaats vindt.

Voor ons is het een voordeel ten opzichte van de moderne DDS dat de module slechts 7 aansluitingen heeft, die zich ook nog op redelijke afstand van elkaar bevinden.

Een moeilijke print met veel ontkoppelingen en moeilijke montage zijn daardoor niet nodig.

Een moderne DDS zoals de AD9951 heeft voor de zelfde faseruis eigenschapen een schone klok van 400 MHz nodig, wat ook de nodige kopzorgen kan opleveren.

Goedkope uitvoeringen van de Si570 zijn bruikbaar tot 160 MHz (CMOS) en 280 MHz (LVDS) deze kosten afhankelijk waar gekocht tussen de 10 en 20 euro.

De duurste uitvoering zijn waarschijnlijk geselecteerde exemplaren en volgens geruchten kosten deze indien verkrijgbaar ongeveer 80 euro.

Deze kunnen dan wel continu afgestemd worden tot 945 MHz en nog in twee niet aaneen gesloten bandjes (VCO/4 = 1212,5<>1417 en VCO/5 = 970<>1134 MHz).

Deze module is niet zoals een DDS zondermeer geschikt voor continu afstemming, maar met slimme software kan dit heel goed opgelost worden.

Alleen in een beperkt gebied (+/-3500 ppm) kan continu worden afgestemd en daarna moet het geheel opnieuw ingesteld worden, wat maximaal 10 ms duurt en dus een onderbreking van het signaal veroorzaakt.

Het programmeren van deze module is voor een vaste frequentie met behulp van wat rekenwerk niet echt moeilijk, maar bij continu afstemming wordt het aanmerkelijk ingewikkelder.

Immers als het bereik van de fijnafstemming wordt overschreden moet er overgeschakeld worden naar de uitgebreide afstemmode en bij overschrijding van het VCO bereik moet er een ander deeltal achter de VCO ingesteld worden en dan het VCO naar een nieuwe instelling die exact de zelfde frequentie als resultaat heeft.

Dit alles moet zeer snel tussen twee afstemstappen worden omgerekend en dat vraagt toch wel om een snelle microcontroller liefst in assembler geprogrammeerd.

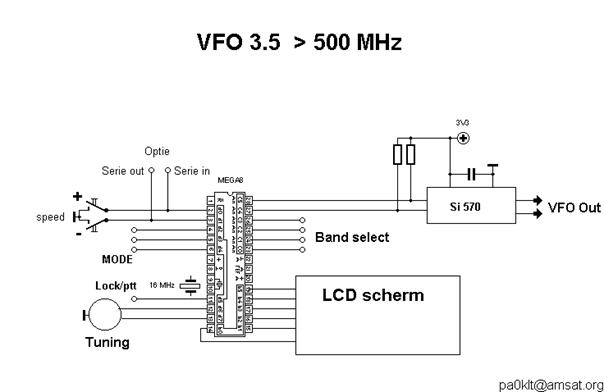

De nu werkende proefschakeling rekent na elke afstemstap geheel opnieuw het afstem getal voor de Si570 uit,wat dan uiteraard via de I2C bus ingeladen moet worden.

De software kan meer dan 1000 stappen per seconde verwerken en dus snel genoeg voor de meeste afstem encoders.

Er zijn op internet aanbiedingen die deze module gebruiken, vooral met USB sturing vanuit de computer.

Zie ook het artikel van Jan Verduyn in de nieuwsbrief 126.

Omdat er volgen mij zeer veel toepassingen zijn te vinden voor de Si570 en natuurlijk ook om de uitdaging, vind ik het belangrijk mijn eigen software hier voor de ontwikkelen.

Als toepassingen denk ik naast HF/VHF en UHF ook aan een signaalgenerator, dubbeltoongenerator en een antenne analyser.

Als eerste ben ik nu bezig een prototype te ontwikkelen van een universeel VFO, uiteraard met programmeerbare MF en mode shift.

De module geeft een digitaal uitgangsignaal.

De CMOS uitvoering een enkele uitgang op CMOS nivo dus voedingspanning (3,3 volt) top/top.

De LVDS Uitvoering heeft twee simmetrische uitgangen, van 0,7 volt top/top.

Deze modules zijn dus uitermate geschikt om een digitale mixer aan te sturen en over het aansturen van een analoge mixer wordt in amateur-kringen nog verschillend gedacht.

Mijn ervaring is echter dat dit zonder problemen (eventueel via een LPF) kan worden toegepast.

Bij serieuze belangstelling komt er een uitgewerkt ontwerp van dit VFO eventueel met print.

De software en hardware zijn nog in ontwikkeling en kunnen dus aangepast worden aan suggesties.

In de toekomst wil ik meer ontwerpen maken met de Si570 en deze mogelijk publiceren.

Ton Blokker

- 1 http://www.box73.de/catalog/

- 2 https://www.silabs.com/Support%20Documents/TechnicalDocs/si570.pdf

- 3 http://images.rfdesign.com/files/4/1100Appel34.pdf

- 4 http://www.holmea.demon.co.uk/FracN/Synth.htm

- 5 http://ocw.mit.edu/NR/rdonlyres/Electrical-Engineering-and-Computer-Science/6-776Spring-2005/B8EFFB02-931B-4953-8BEE-B1C2A9A1B4EA/0/lec21.pdf

- 6 Artikel: Fractionele N synthese (radio) elektronica november 1992

- 7 http://t03dsp.skydan.in.ua/Download.htm

- 8 http://en.wikipedia.org/wiki/CPLD